# PCI SIG

### Advanced Techniques for PCle 3.0 Receiver Testing

Michael Fleischer-Reumann BERTs Portfolio Planner Agilent Technologies

<u>Presentation Disclaimer</u>: All opinions, judgments, recommendations, etc. that are presented herein are the opinions of the presenter of the material and do not necessarily reflect the opinions of the PCI-SIG<sup>®</sup>.

- From PCIe 2.x to PCIe 3.0

- Test Set-up and Calibration Methodology according to Base Specification

- Practical set-up

- Step-by-step Calibration Procedure

- Summary

- Q&A

### From PCIe 2.x to PCIe 3.0 -Goals and Consequences

- G Effective data rate shall be doubled

- Existing infrastructure of PCs and servers shall be reusable; in PCIe terminology this means:

- ✓ PCIe 2.x compliant channels shall also be compliant with PCIe 3.0

- Transmitting data at higher rate over the same channels means more loss causing closed eyes at the end of channel / receiver (RX) input

- Method needs to be found opening the signal eye in order to

- ✓ asses channel compliance

- ✓ achieve functionality

- Circuits and methods compensating channel loss have to be implemented in active components, Transmitter (TX) and Receiver (RX)

- ✓ enhancing TX de-emphasis range and adding pre-shoot not sufficient

- ⇒ extensive RX equalization is necessary to achieve functionality

- open source simulation tool (seasim) provides turnkey capability for channel assessment, where the user provides the channel characteristics at the receiver's die pad as step responses, and the tool calculates a statistical eye showing pass/fail.

Ο

a

S

n

S

e

q

U

e

n

С

e

S

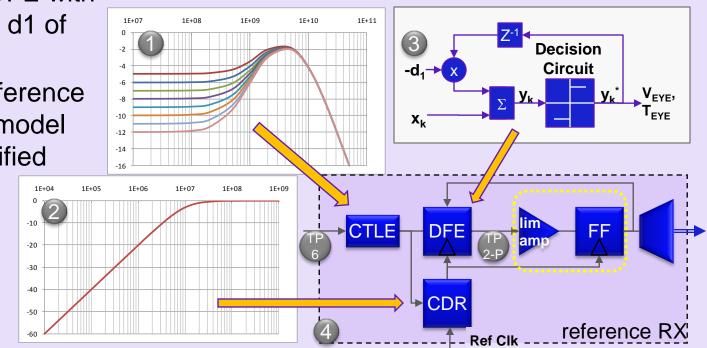

## Reference Receiver with Equalization

- 1. CTLE with seven "DC-attenuation" settings peaking at 4 GHz

- 2. Reference CDR specified by OJTF with no peaking and 10MHz BW

- One tap DFE with a limit for d1 of +/- 30mV

- П-type reference package model also specified

Eye opening is specified for basic RX inside orange dotted box

- From PCIe 2.x to PCIe 3.0

- Test Set-up and Calibration Methodology according to Base Specification

- Practical set-up

- Step-by-step Calibration Procedure

- Summary

- Q&A

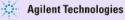

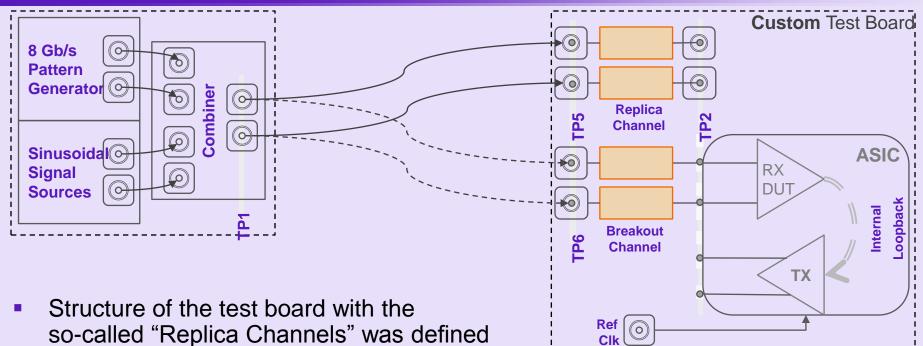

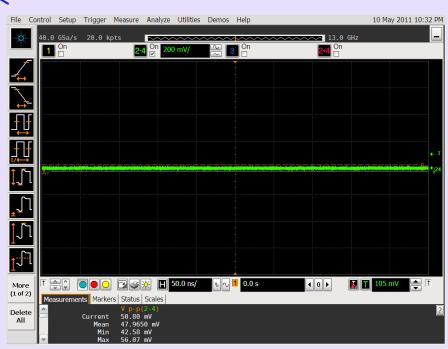

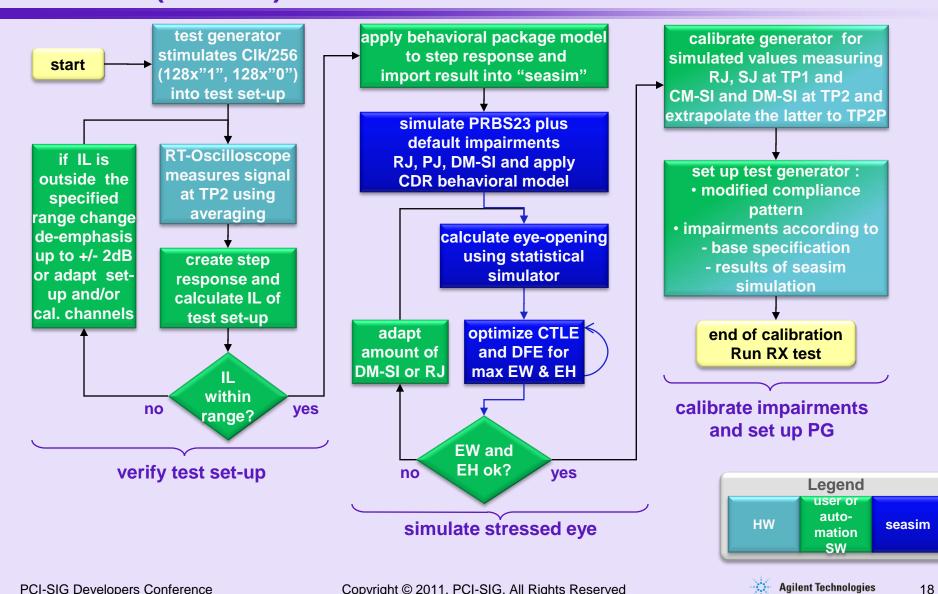

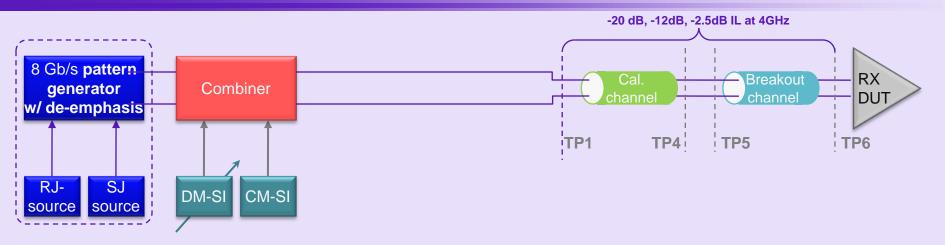

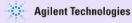

### RX Test for PCle 3.0 Generic Test Set-up

- RX input is stimulated from a BERT PG with a "stressed eye" signal containing well defined impairments

- RX-output is looped back through the device's TX such that the RX's "correct" detection can be observed with a Bit Error Ratio Tester (BERT)

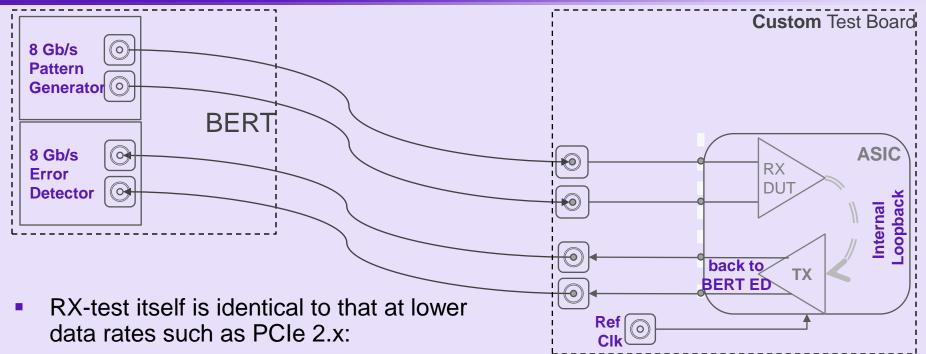

- Construction / calibration of RX stress test signal is completely different utilizing methods and tools originally created for channel compliance verification

- generating the required Sinusoidal and Random Jitter (SJ and RJ)

- It is complemented with signal sources for the simultaneous generation of Common- and Differential Mode Sinusoidal Interference (CM- and DM-SI) modeling the "noise" of the real application

- They are superimposed to the test pattern through a passive combiner; output at TP1

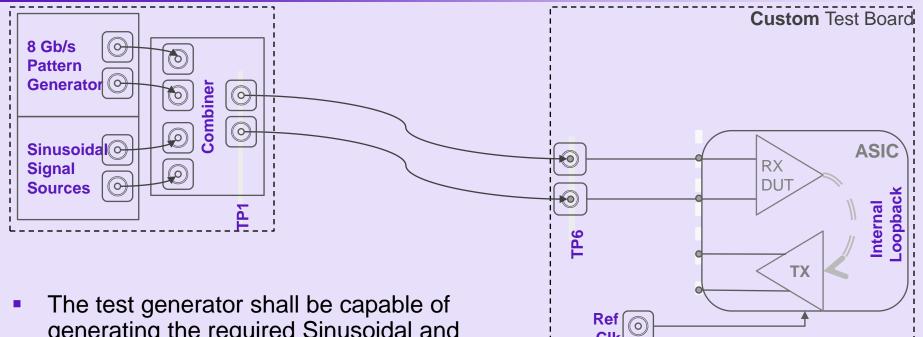

- Is TP6 suited for the calibration of the stressed eye RX-test signal?

PCI-SIG Developers Conference

Copyright © 2011, PCI-SIG, All Rights Reserved

- The PC board traces enabling connection of the DUT with test equipment (the so-called breakout channels) are not negligible in terms of signal degradation (DDJ) / (ISI)

- Calibration must include the breakout channels

- Connecting or probing for calibration of the stress signal directly at the ASIC pins / balls is not practical!

- At the output of those there is the important test point TP2

- TP2 is equivalent to the ASIC-input pins / balls as the replica channels duplicate the break-out channels

- TP2 is the "closest point" to the RX inputs that can be measured of the RX test signals

#### RX Test Specifications for Stressed Jitter Eye

| Symbol                        | Parameter                   | Limits at 8.0 GT/s   | Units             | Comments                                                                           |

|-------------------------------|-----------------------------|----------------------|-------------------|------------------------------------------------------------------------------------|

| V <sub>RX-LAUNCH-</sub><br>8g | Generator<br>launch voltage | 800 (nominal)        | mV <sub>PP</sub>  | Measured at TP1,                                                                   |

| T <sub>RX-UI-8G</sub>         | Unit Interval               | 125.00               | ps                | Nominal value is sufficient for Rx tolerancing.<br>Value does not account for SSC. |

| V <sub>RX-SV-8G</sub>         | Eye height at TP2P          | 25 (min)<br>35 (max) | mV <sub>PP</sub>  | At BER=10 <sup>-12</sup>                                                           |

| T <sub>RX-SV-8G</sub>         | Eye width at TP2P           | 0.30                 | UI                | At BER=10 <sup>-12</sup>                                                           |

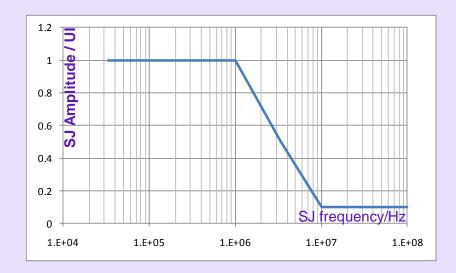

| T <sub>RX-ST-SJ-8G</sub>      | Sinusoidal Jitter           | 0.1 – 1.0            | UI <sub>PP</sub>  | Measured at TP1.                                                                   |

| T <sub>RX-SVRJ-8G</sub>       | Random Jitter               | 3.0                  | ps <sub>RMS</sub> | RJ spectrally flat before filtering. Measured at TP1. Adjusted to set eye width    |

#### RX Test Specifications for Stressed Voltage Eye

| Symbol                     | Parameter                                      | Limits at 8.0 GT/s                                                   | Units             | Comments                                                                                                                                                                                  |

|----------------------------|------------------------------------------------|----------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>RX-LAUNCH-8G</sub>  | Generator<br>launch voltage                    | 800                                                                  | mV <sub>PP</sub>  | Measured at TP1 Figure 4-65.<br>VRX-LAUNCH-8G may be adjusted if necessary to<br>yield the proper EH as long as the outside eye<br>voltage at TP2 does not exceed 1300 mV <sub>PP</sub> . |

| T <sub>RX-UI-8G</sub>      | Unit Interval                                  | 125.00                                                               | ps                | Nominal value is sufficient for Rx tolerancing. Value does not account for SSC.                                                                                                           |

| V <sub>RX-SV-8G</sub>      | Eye height at TP2P                             | 25 (-20 dB channel)<br>50 (-12 dB channel)<br>200 (-3 dB channel)    | mV <sub>PP</sub>  | Eye height @ BER=10 <sup>-12</sup>                                                                                                                                                        |

| T <sub>RX-SV-8G</sub>      | Eye width at TP2P                              | 0.3 to 0.35                                                          | UI                | Eye width at BER=10 <sup>-12</sup> .                                                                                                                                                      |

| V <sub>RX-SV-DIFF-8G</sub> | Differential mode<br>interference              | 14 or greater                                                        | mV <sub>PP</sub>  | Adjusted to set EH. Frequency = 2.10 GHz                                                                                                                                                  |

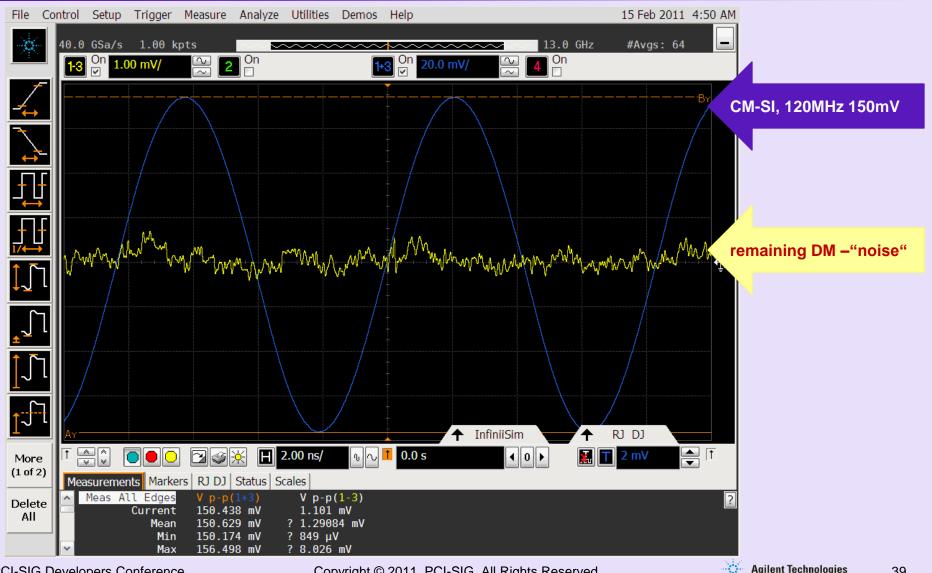

| V <sub>RX-SV-CM-8G</sub>   | Rx AC Common mode<br>voltage at 120MHz at TP2P | 150 (EH < 100 mV <sub>PP</sub> )<br>250 (EH ≥ 100 mV <sub>PP</sub> ) | $mV_{PP}$         | Defined for a single tone at 120 MHz.                                                                                                                                                     |

| T <sub>RX-SV-SJ-8G</sub>   | Sinusoidal Jitter at 100<br>MHz                | 0.1                                                                  | UI <sub>PP</sub>  | Fixed at 100 MHz.                                                                                                                                                                         |

| T <sub>RX-SVRJ-8G</sub>    | Random Jitter                                  | 2.0                                                                  | ps <sub>RMS</sub> | Rj spectrally flat before filtering.                                                                                                                                                      |

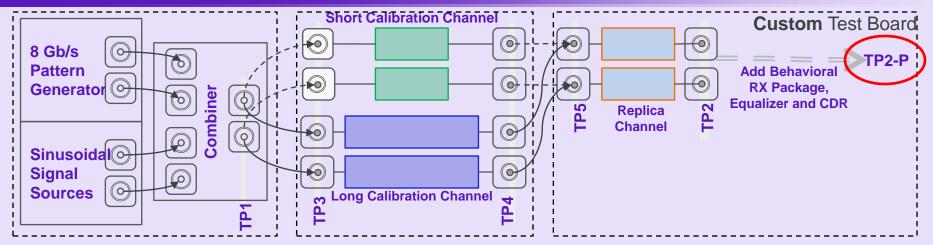

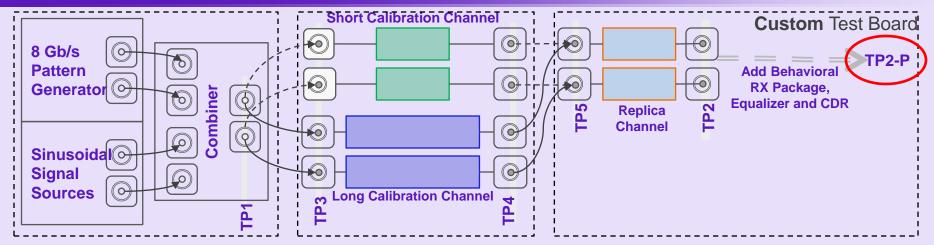

### Calibration Method of Stressed Eye for RX Test

- When using long calibration channel signal eye at TP2 is completely closed

- Specifying stressed eye or jitter components at TP2 is therefore impractical

- Specification of minimal tolerable eye opening refers to input of "basic receiver" inside the ASIC behind the reference RX's equalization (CTLE and DFE) and "jitter-filtering" with OJTF of RX-CDR (post processed signal of TP2 resulting in the signal at virtual test point TP2-P)

- ⇒ Calibration by measurement *only* is not possible

- ⇒ Combination of signal *measurements* and SW-simulation is required

### Calibration Method of Stressed Eye for RX Test

- Measure the actual RX test pattern with all signal impairments at TP2 and use SW to calculate the eye opening at TP2-P (applying package- and CDR- behavioral model and optimizing reference RX equalizers)

- Adjust the relevant impairments (such as DM-SI or RJ) on the test generator until the specified eye-height or eye-width is achieved

- Noise floor of RT-scope decreases eye-opening vertically and (through voltage-noise to jitter conversion) horizontally as well such that the resulting stress signal would be wider open than "measured" and the RX under test would not be stressed as much as intended

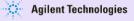

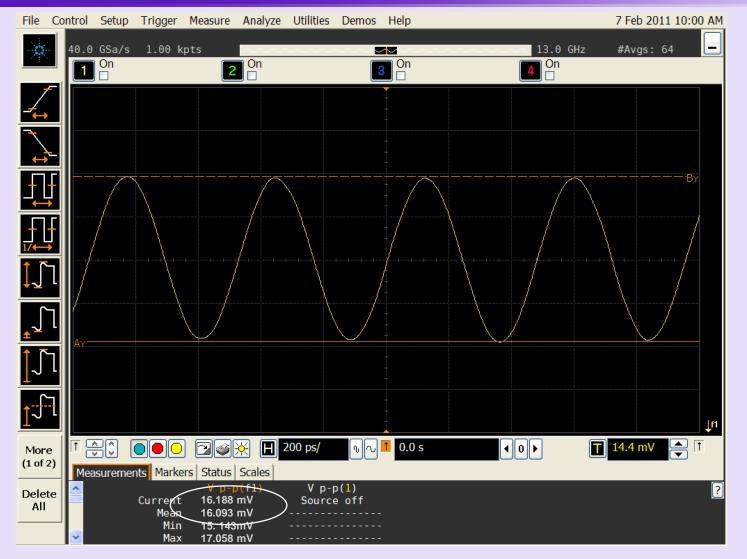

### Screenshots of test pattern with Agilent Technologies impairments turned on

- Same scope setting 200mV/div

- Pattern paused "visualizing" DM-SI of 14mV<sub>pp</sub> at 2.1GHz

- Reading of approx. 50mVpp !

- Compliance pattern (800mV,pp) superimposed with DM-SI of 14mV<sub>pp</sub> at 2.1GHz

- Scope setting 200mV/div (diff.) and a noise floor of approx. 4.7mV<sub>rms</sub> (diff.)

⇒ Accurate measurement of the stress signal at TP2 is impractical and error prone

### Calibration Method of Stressed Eye for RX Test

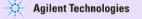

- Divide the calibration of the RX stress signal into three separate steps:

- 1. Characterize the test set-up at TP2 using a test signal (clock/256), which allows averaging for noise reduction of RT-scope, resulting in a measured "step-response"

- Use this step response as input for the statistical simulation SW that is also used for channel compliance verification and that calculates the eye opening for the final stress test signal (PRBS23) at a probability level of 10<sup>-12</sup> after optimizing all equalizers and simulating impairments, iteratively finding the necessary amount of DM-SI or RJ that yields the specified eye-height (EH) or eye-width (EW)

- 3. Calibrate those impairments, which require calibration, one at a time, at the best suited test-point with the best suited test signal

- Perform RX test with modified compliance pattern and all impairments turned on

#### Calibration of Stressed Eye for RX Test Flow chart w/ Statistical Eye Analysis Simulator SIG (seasim)

**PCI-SIG Developers Conference**

Copyright © 2011, PCI-SIG, All Rights Reserved

- From PCIe 2.x to PCIe 3.0

- Test Set-up and Calibration Methodology according to Base Specification

- Practical set-up

- Step-by-step Calibration Procedure

- Summary

- Q&A

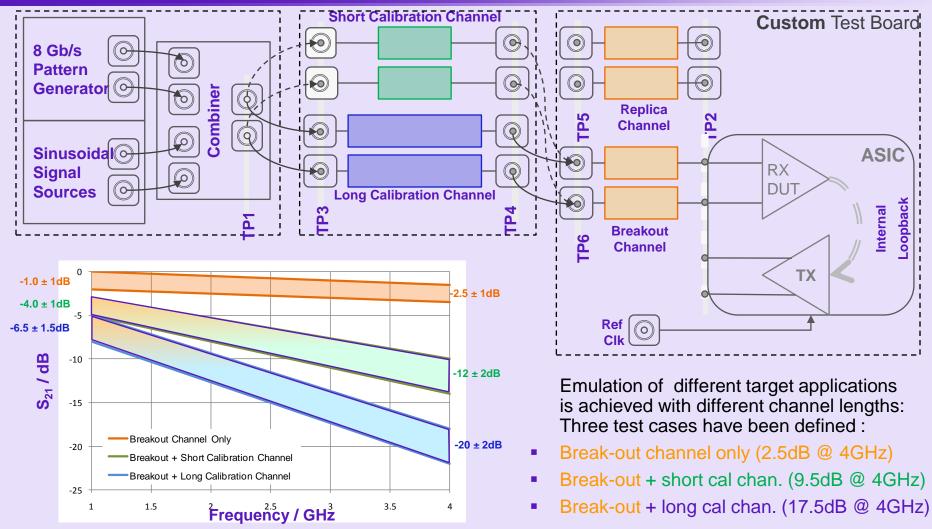

#### Two different RX Test Set-Ups (1 of 2) Stressed Jitter Eye

- Stressed *jitter* eye is testing RX for minimum horizontal eye opening (for long calibration channel plus break-out channel only)

- Horizontal eye closure adjusted varying RJ

- SJ varied according to specified curve

- This set up is straight forward and can be realized with suitable BERTs

#### Two different RX Test Set-Ups (2 of 2) Stressed Voltage Eye

- Stressed voltage eye is testing RX for minimum vertical eye opening (three possible combinations of calibration- plus break-out- channels)

- Vertical eye closure is adjusted varying DM-SI

- This test requires at least two additional voltage sources plus the non-trivial combiner circuit

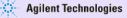

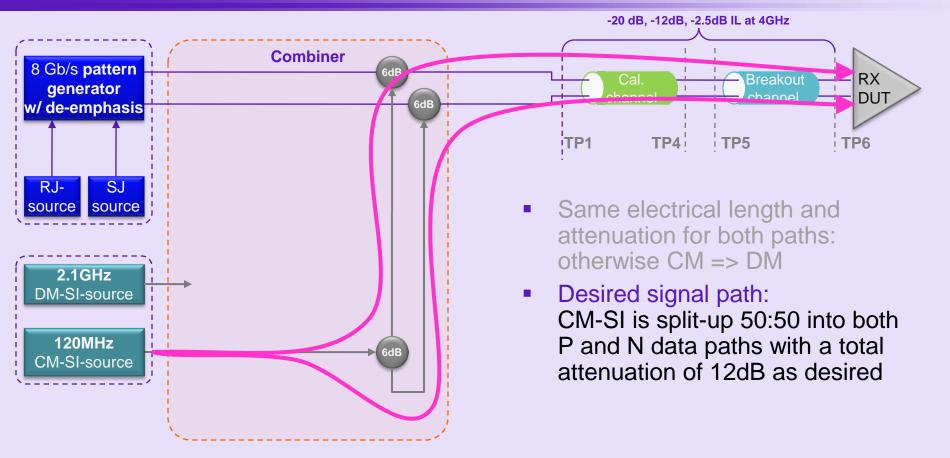

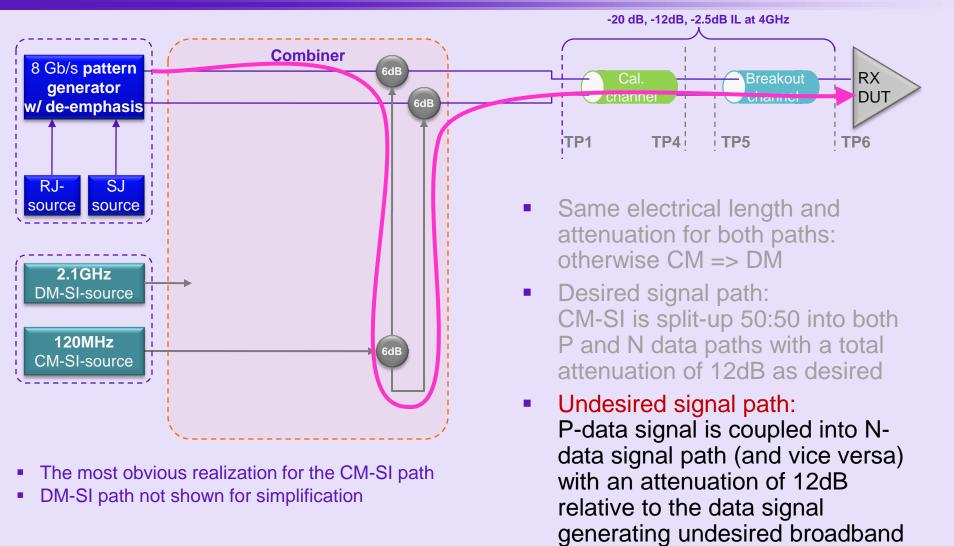

#### Realization for Voltage Interference Sources and Combiner

- The most obvious realization for the CM-SI path

- DM-SI path not shown for simplification

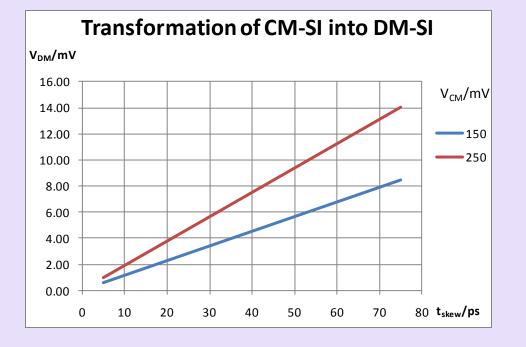

### Transformation of CM- to DM-SI due to skew between "P" and "N"

$$\begin{array}{ll} \mathsf{V}_{\mathsf{DM}}\left(t\right) &= \mathsf{V}_{\mathsf{CM},\mathsf{amp}} \; x \; \{ \sin[\omega_{\mathsf{CM}} t] - \sin[\omega_{\mathsf{CM}}(t - t_{\mathsf{skew}}])] \} \\ &= 2 \; x \; \cos((x + y)/2) \; x \; \sin((x - y)/2) \\ &= 2 \; x \; \mathsf{V}_{\mathsf{CM},\mathsf{amp}} \; x \; \cos(\omega_{\mathsf{CM}}(t - t_{\mathsf{skew}}/2)) \; x \; \sin(\omega_{\mathsf{CM}} t_{\mathsf{skew}}/2) \\ &= 2 \; x \; \mathsf{V}_{\mathsf{CM},\mathsf{amp}} \; x \; \cos(\omega_{\mathsf{CM}}(t - t_{\mathsf{skew}}/2)) \; x \; \sin(\omega_{\mathsf{CM}} t_{\mathsf{skew}}/2) \\ &= 2 \; x \; \mathsf{V}_{\mathsf{CM},\mathsf{amp}} \; x \; \sin(\pi \; x \; f_{\mathsf{CM}} \; x \; t_{\mathsf{skew}}) \end{array}$$

In addition to DM-SI resulting from skew between the two sinewaves there is also DM-SI resulting from different amplitudes of the two sinewaves, which is directly proportional to amplitude and attenuation differences

#### Realization for Voltage Interference Sources and Combiner

- The most obvious realization for the CM-SI path

- DM-SI path not shown for simplification

#### Realization for Voltage Interference Sources and Combiner

Copyright © 2011, PCI-SIG, All Rights Reserved

(DC-coupled) crosstalk

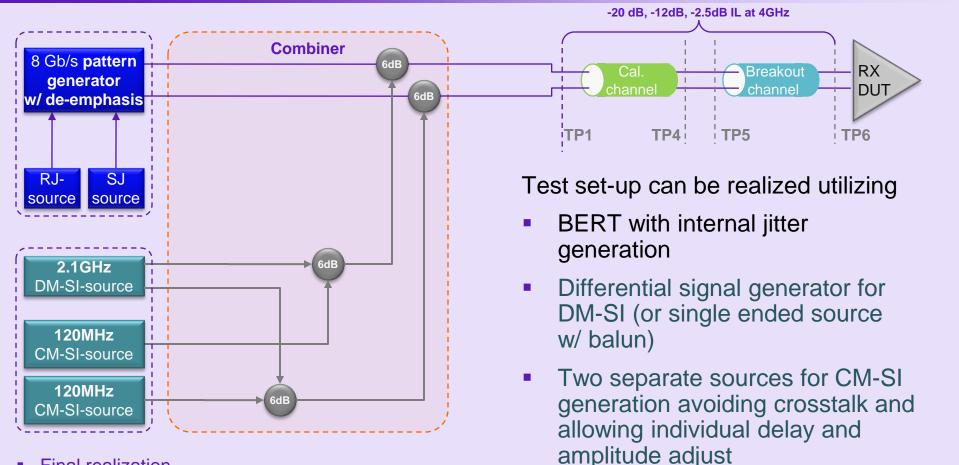

#### **Realization for Voltage Interference** SIG **Sources and Combiner**

**Final realization**

External "plumbing" for signal

addition

- From PCIe 2.x to PCIe 3.0

- Test Set-up and Calibration Methodology according to Base Specification

- Practical set-up

- Step-by-step Calibration Procedure

- Summary

- Q&A

#### Interpretation of Calibration Channel Specification

#### 4.3.4.3.1. Calibration Channels

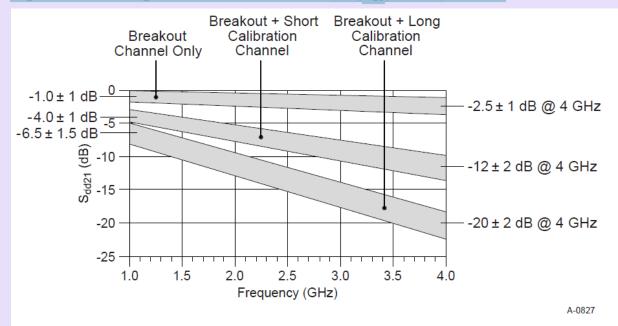

The calibration channel's electrical characteristics are defined in terms of differential insertion loss masks as shown in Figure 4-66, with  $S_{21}$  measured between TP1 and TP2. Any HF loss caused by the generator and combiner and the connections between TP1-TP3 and TP4-TP5 that represent cabling are to be included in the  $S_{21}$  measurement.

#### Long Cal. Channel with 0dB and -1.5dB De-emphasis

1. Check IL of test set-up: differentiating step response and doing FFT of the resulting impulse response

- 2. Measured IL too large (~21.5dB)!

- 3. Correct with appropriate deemphasis of -1.5dB of post cursor and adjust amplitude for same end value of step response

- 4. Insertion loss of adjusted set-up ~ 20.0dB

PCI-SIG Developers Conference

Copyright © 2011, PCI-SIG, All Rights Reserved

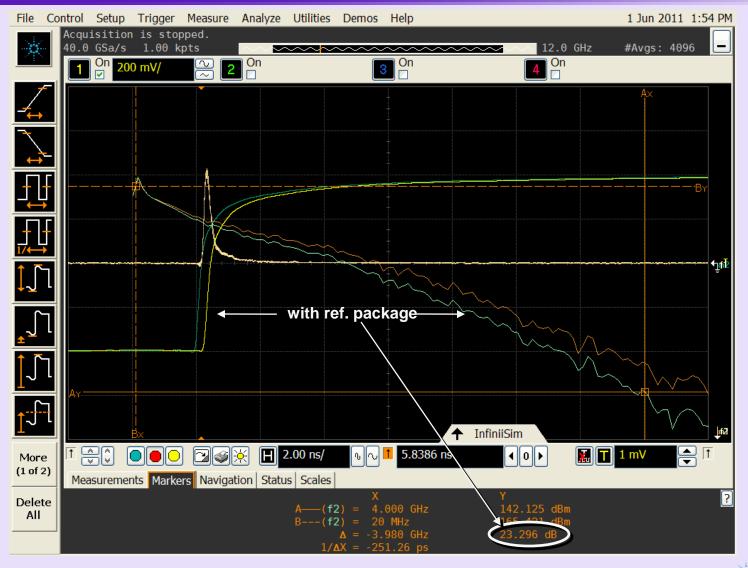

#### Long Cal. Channel + Ref. Package

Apply the reference package model (IL @ 4GHz ~ 3.2dB) and import waveform in appropriate form into seasim!

PCI-SIG Developers Conference

Copyright © 2011, PCI-SIG, All Rights Reserved

# Construction and Calibration

- Disconnect all signals from scope input (terminate with 50 Ohms)

- 1. Measure\* scope intrinsic noise  $V_{n,intrinsic}$

- Turn on all sources, set generator to "pause"-pattern / set amp=0V ("disable" outputs)

- 2. Measure\* Noise Voltage  $V_{n,system}$  and determine noise of generators as  $V_{n,gen} = sqrt (V_{n,intrinsic}^2 V_{n,system}^2)$

\* always apply ref. package model

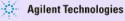

### **Differential Noise Voltage**

- Scope Noise  $V_{n,intrinsic} = 640 \ \mu V_{rms}$

- System Noise =  $V_n = 754 \mu V_{rms}$

- $V_{n,gen} = sqrt (V_{n,intrinsic}^2 V_{n,system}^2) = 399 \ \mu V_{rms}$

SIG

### Seasim Parameters

|                      | 🚺 my-pcie-gen3-N.inc - Notepad                                                       |                          |                                                                                                                                                                                                                               |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                      | File Edit Format View Help                                                           |                          |                                                                                                                                                                                                                               |  |  |  |  |

|                      | <pre># This contains all of the default settings for Gen3 # channel compliance</pre> |                          |                                                                                                                                                                                                                               |  |  |  |  |

|                      | ui<br>scale_ypdf<br>nui<br>isi_xtalk_ratio<br>aggr_align<br>BER                      | 2.0<br>80<br>4<br>center | <pre># Time in secs # ratio of equalized step to output PDF # Search length back from cursor # Ratio vpt to max ISI and Xtalk magnitude # Align all aggressors to peak of eye opening # BER used to measure eye opening</pre> |  |  |  |  |

|                      | jit_seconds                                                                          | True                     | # Allow seconds to specify jitter values                                                                                                                                                                                      |  |  |  |  |

|                      | adapt_DC<br>adapt_pole<br>adapt_Cspace<br>adapt_FOM<br>adapt_DFE_mag                 | 24<br>area               | -9,-8,-7,-6] # DC gain of CTLE in dB<br># CTLE fixed pole location<br># Coefficent space size<br># eye height * eye width FOM<br># Number and dynamic range of DFE taps                                                       |  |  |  |  |

|                      | leq_bw<br>max_ds_offset                                                              | 8e9<br>0.1               | # HF roll-off of equalizer<br># Maximum data sample offset center in UI                                                                                                                                                       |  |  |  |  |

| RJ →                 | jit_lfrj                                                                             | 2.0e-12                  | # Gaussian sigma post channel jitter                                                                                                                                                                                          |  |  |  |  |

| SJ →                 | jit_lfudj                                                                            | 12.5e-12                 | # Sinusoidal Jitter                                                                                                                                                                                                           |  |  |  |  |

| DM-SI →              | vn_lfudn                                                                             | 14e-3                    | <pre># pk-pk uniform deterministic voltage noise</pre>                                                                                                                                                                        |  |  |  |  |

| V <sub>n,gen</sub> → | vn_lfrn                                                                              | 0.4e-3                   | # intrinsic noise                                                                                                                                                                                                             |  |  |  |  |

|                      | •                                                                                    |                          |                                                                                                                                                                                                                               |  |  |  |  |

PCI

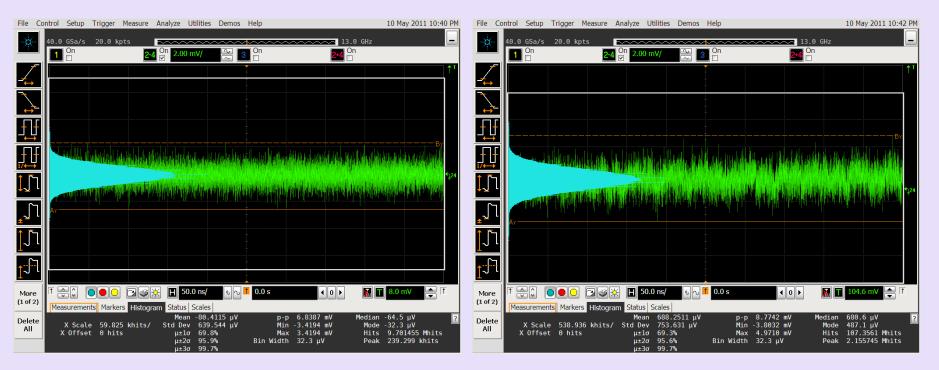

## Seasim calibration for stressed voltage test, long cal channel

starting value for DM-SI = 14mVresulting in ~27mV of eye height (EH) "SW-adjusted" value for DM-SI = 16mV resulting in ~25mV of EH w/ (0.3UI<EW<0.35UI)

# Construction and Calibration

- Disconnect all signals from scope input (terminate with 50 Ohms)

- 1. Measure\* scope intrinsic noise V<sub>n,intrinsic,rms</sub>

- Turn on all sources, set generator to "pause"-pattern / set amp=0V ("disable" outputs)

- 2. Measure\* Noise Voltage V<sub>n,system</sub> and determine noise of generators as V<sub>n,gen</sub> = sqrt (V<sub>n,intrinsic</sub><sup>2</sup> - V<sub>n,system</sub><sup>2</sup>)

- 3. Adjust\* DM-SI voltage amplitude to value resulting from Seasim

\* always apply ref. package model (package loss at 2.1 GHz approximately 1.7dB)

Copyright © 2011, PCI-SIG, All Rights Reserved

As  $V_{n,gen}$  (noise from generator) is taken care of by vn\_lfrn in seasim, averaging can be used for calibration of DM-SI

# Construction and Calibration

- 1. Measure\* scope intrinsic noise V<sub>n,intrinsic,rms</sub>

- Turn on all sources, set generator to "pause"-pattern / set amp=0V ("disable" outputs)

- 2. Measure Noise Voltage  $V_{n,system}$  and determine noise of generators as  $V_{n,gen} = sqrt (V_{n,intrinsic}^2 V_{n,system}^2)$

- Adjust DM-SI voltage amplitude to value resulting from Seasim applying ref. package model (package loss at 2.1 GHz approximately 1.7dB)

- Adjust CM-SI amplitude to specified value (150 or 250mV) (also applying ref package model) adjust delay (and amplitudes) of CM-SI generator for minimum residual differential amplitude

\* always apply ref. package model

#### **CM-SI** calibration of SIG residual DM

**PCI-SIG Developers Conference**

Copyright © 2011, PCI-SIG, All Rights Reserved

**Agilent Technologies**

# Construction and Calibration

- Disconnect all signals from scope input (terminate with 50 Ohms)

- 1. Measure\* scope intrinsic noise V<sub>n,intrinsic,rms</sub>

- Turn on all sources, set generator to "pause"-pattern / set amp=0V ("disable" outputs)

- 2. Measure\* Noise Voltage  $V_{n,system}$  and determine noise of generators as  $V_{n,gen} = sqrt (V_{n,intrinsic}^2 - V_{n,system}^2)$

- Adjust\* DM-SI voltage amplitude to value resulting from Seasim applying ref. package model (package loss at 2.1 GHz approximately 1.7dB)

- Adjust\* CM-SI amplitude to specified value (150 or 250mV) (also applying ref package model) adjust delay (and amplitudes) of CM-SI generator for minimum residual differential amplitude

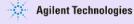

- ✓ Set generator to clock/2 pattern

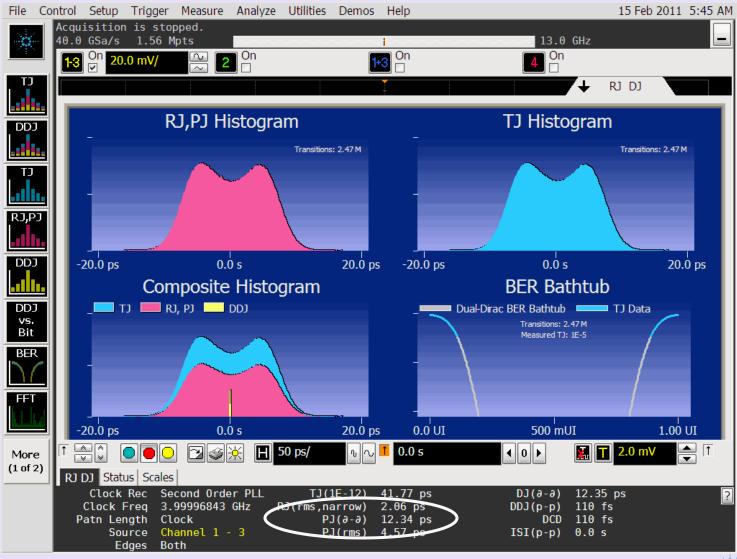

- 5. Turn on RJ and SJ each at a time and sequentially adjust\* them to specified values measuring either at TP1 or TP2

- always apply ref. package model

\*

PCI-SIG Developers Conference

Copyright © 2011, PCI-SIG, All Rights Reserved

Agilent Technologies

### **Calibration of RJ and SJ**

PCI-SIG Developers Conference

PCI

SIG

Copyright © 2011, PCI-SIG, All Rights Reserved

42

-0-

### Calibration accomplished ready to perform the RX test

- Disconnect cables fromTP5 (input replica channel) and connect to TP6 (input breakout channel)

- Set DUT-RX into loopback

- Turn on all impairments as calibrated and make BERT-PG generate the test pattern (modified compliance pattern)

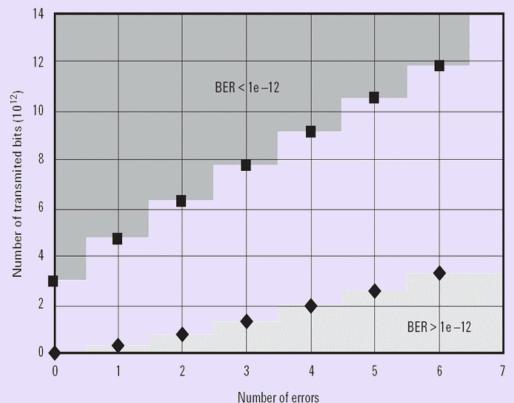

- Verify number of errors for sufficient time period such that BER<10<sup>-12</sup> w/ 95% of CL e.g.: 0 errors in 6¼ minutes 1 error in 10¼ minutes 2 errors in ...

- From PCle 2.x to PCle 3.0

- Test Set-up and Calibration Methodology according to Base **Specification**

- **Practical set-up**

- **Step-by-step Calibration Procedure**

- Summary

- A&Q

- PCIe 3.0 Phy Layer system design with its 8GT/s was relatively demanding, its realization in a computer system is not trivial

- Interoperability depends on proper RX functionality and can only be guaranteed by thorough RX testing

- Test set-up must be designed with great care

- Calibration of stress test signal requires deep insight into base specification and measurement techniques

- Performing "step-by-step calibration" manually is cumbersome and error prone – automation desirable

- From PCIe 2.x to PCIe 3.0

- Test Set-up and Calibration Methodology according to Base Specification

- Practical set-up

- Step-by-step Calibration Procedure

- Summary

- Q&A

## Thank you for attending the PCI-SIG Developers Conference 2011.

### For more information please go to www.pcisig.com

PCI-SIG Developers Conference

Copyright © 2011, PCI-SIG, All Rights Reserved